# LTC6090/LTC6090-5

# 140V CMOS Rail-to-Rail Output, Picoamp Input Current Op Amp

### DESCRIPTION

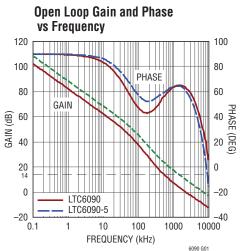

The LTC®6090/LTC6090-5 are high voltage, precision monolithic operational amplifiers. The LTC6090 is unity gain stable. The LTC6090-5 is stable in noise gain configurations of 5 or greater. Both amplifiers feature high open loop gain, low input referred offset voltage and noise, and pA input bias current and are ideal for high voltage, high impedance buffering and/or high gain configurations.

The amplifiers are internally protected against overtemperature conditions. A thermal warning output, TFLAG, goes active when the die temperature approaches 150°C. The output stage may be turned off with the output disable pin OD. By tying the OD pin to the thermal warning output (TFLAG), the part will disable the output stage when it is out of the safe operating area. These pins easily interface to any logic family.

Both amplifiers may be run from a single 140V or spit  $\pm$ 70V power supplies and are capable of driving up to 200pF of load capacitance. They are available in either an 8-lead SO or 16-lead TSSOP package with exposed pad for low thermal resistance.

**Δ7**, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

### FEATURES

- Supply Range: ±4.75V to ±70V (140V)

- 0.1Hz to 10Hz Noise: 3.5µV<sub>P-P</sub>

- Input Bias Current: 50pA Maximum

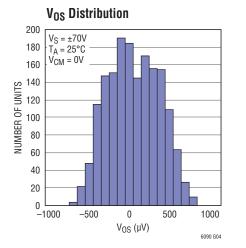

- Low Offset Voltage: 1.25mV Maximum

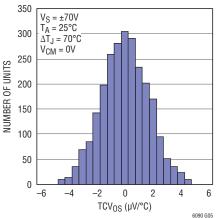

- Low Offset Drift: ±5µV/°C Maximum

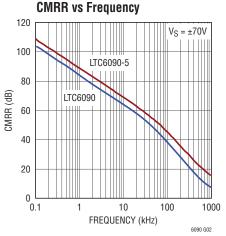

- CMRR: 130dB Minimum

- Rail-to-Rail Output Stage

- Output Sink and Source: 50mA

- 12MHz Gain Bandwidth Product

- 21V/µs Slew Rate

- 11nV/√Hz Noise Density

- Thermal Shutdown

- Available in Thermally Enhanced SOIC-8E or TSSOP-16E Packages

# **APPLICATIONS**

- ATE

- Piezo Drivers

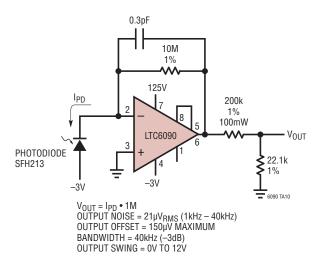

- Photodiode Amplifier

- High Voltage Regulators

- Optical Networking

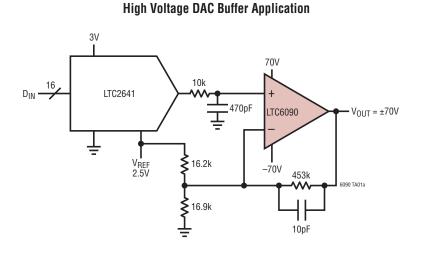

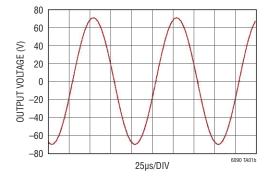

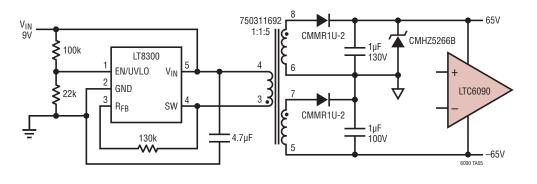

# TYPICAL APPLICATION

#### 140V<sub>P-P</sub> Sine Wave Output

LINEAR TECHNOLOGY

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> )<br>COM |                                                | Outpı<br>Co |

|-----------------------------------------------------------------|------------------------------------------------|-------------|

| Input Voltage                                                   |                                                | Opera       |

| <u>OD</u>                                                       | V <sup>-</sup> to V <sup>+</sup> + 0.3V        | (Note       |

| +IN, –IN,                                                       | V <sup>-</sup> – 0.3V to V <sup>+</sup> + 0.3V | Speci       |

| OD to COM                                                       | 3V to 7V                                       | LT          |

| Input Current                                                   |                                                | LT          |

| +IN, –IN                                                        | ±10mA                                          | LT          |

| TFLAG Output                                                    |                                                | Junct       |

| TFLAG                                                           | $V^{-} - 0.3V$ to V <sup>+</sup> + 0.3V        | Stora       |

| TFLAG to COM                                                    | 3V to 7V                                       | Lead        |

|                                                                 |                                                |             |

| Output Current                                |

|-----------------------------------------------|

| Continuous (Note 2)                           |

| Operating Junction Temperature Range          |

| (Note 3)–40°C to 125°C                        |

| Specified Junction Temperature Range (Note 4) |

| LTC6090C0°C to 70°C                           |

| LTC6090I40°C to 85°C                          |

| LTC6090H40°C to 125°C                         |

| Junction Temperature (Note 5) 150°C           |

| Storage Temperature Range–65°C to 150°C       |

| Lead Temperature (Soldering, 10 sec)          |

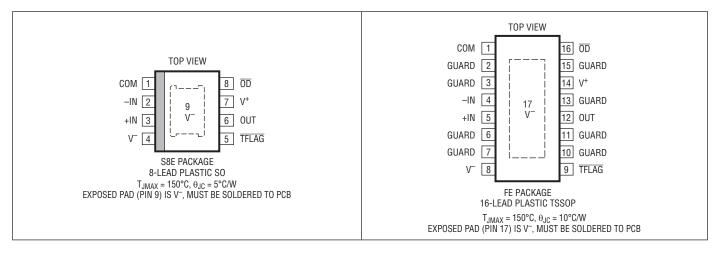

### PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION   | JUNCTION TEMPERATURE RANGE |

|------------------|-------------------|---------------|-----------------------|----------------------------|

| LTC6090CS8E#PBF  | LTC6090CS8E#TRPBF | 6090          | 8-Lead Plastic SO     | 0°C to 70°C                |

| LTC6090IS8E#PBF  | LTC6090IS8E#TRPBF | 6090          | 8-Lead Plastic SO     | -40°C to 85°C              |

| LTC6090HS8E#PBF  | LTC6090HS8E#TRPBF | 6090          | 8-Lead Plastic SO     | -40°C to 125°C             |

| LTC6090CFE#PBF   | LTC6090CFE#TRPBF  | 6090FE        | 16-Lead Plastic TSSOP | 0°C to 70°C                |

| LTC6090IFE#PBF   | LTC6090IFE#TRPBF  | 6090FE        | 16-Lead Plastic TSSOP | -40°C to 85°C              |

| LTC6090HFE#PBF   | LTC6090HFE#TRPBF  | 6090FE        | 16-Lead Plastic TSSOP | -40°C to 125°C             |

# **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION   | JUNCTION TEMPERATURE RANGE |

|-------------------|---------------------|---------------|-----------------------|----------------------------|

| LTC6090CS8E-5#PBF | LTC6090CS8E-5#TRPBF | 60905         | 8-Lead Plastic SO     | 0°C to 70°C                |

| LTC6090IS8E-5#PBF | LTC6090IS8E-5#TRPBF | 60905         | 8-Lead Plastic SO     | -40°C to 85°C              |

| LTC6090HS8E-5#PBF | LTC6090HS8E-5#TRPBF | 60905         | 8-Lead Plastic SO     | -40°C to 125°C             |

| LTC6090CFE-5#PBF  | LTC6090CFE-5#TRPBF  | 6090FE-5      | 16-Lead Plastic TSSOP | 0°C to 70°C                |

| LTC6090IFE-5#PBF  | LTC6090IFE-5#TRPBF  | 6090FE-5      | 16-Lead Plastic TSSOP | -40°C to 85°C              |

| LTC6090HFE-5#PBF  | LTC6090HFE-5#TRPBF  | 6090FE-5      | 16-Lead Plastic TSSOP | -40°C to 125°C             |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications and all typical values are at T<sub>J</sub> = 25°C. Test conditions are V<sup>+</sup> = 70V, V<sup>-</sup> = -70V, V<sub>CM</sub> =  $V_{OUT} = 0V$ ,  $V_{\overline{OD}} = 0$  pen unless otherwise noted.

|                            |                                                                               |                                                                                        |   | C                  | -, I-SUFFIX     | ES                |              | H-SUFFIX        |                   |                   |

|----------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---|--------------------|-----------------|-------------------|--------------|-----------------|-------------------|-------------------|

| SYMBOL                     | PARAMETER                                                                     | CONDITIONS                                                                             |   | MIN                | ТҮР             | MAX               | MIN          | ТҮР             | MAX               | UNITS             |

| V <sub>OS</sub>            | Input Offset Voltage                                                          |                                                                                        | • |                    | ±330<br>±330    | ±1000<br>±1250    |              | ±330<br>±330    | ±1000<br>±1250    | μV<br>μV          |

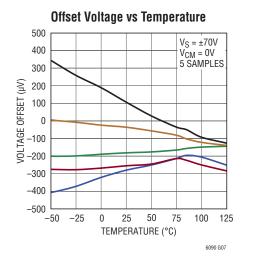

| $\Delta V_{OS} / \Delta T$ | Input Offset Voltage Drift                                                    | $T_A = 25^{\circ}C, \Delta T_J = 70^{\circ}C$                                          |   | -5                 | ±3              | 5                 | -5           | ±3              | 5                 | µV/°C             |

| IB                         | Input Bias Current (Note 6)                                                   | Supply Voltage = $\pm 70V$<br>Supply Voltage = $\pm 15V$<br>Supply Voltage = $\pm 15V$ | • |                    | 3<br>0.3        | 50                |              | 3<br>0.3        | 800               | pA<br>pA<br>pA    |

| I <sub>OS</sub>            | Input Offset Current (Note 6)                                                 | Supply Voltage = ±15V                                                                  | • |                    | 0.5             | 30                |              | 0.5             | 120               | pA<br>pA          |

| e <sub>n</sub>             | Input Noise Voltage Density                                                   | f = 1kHz<br>f = 10kHz                                                                  |   |                    | 14<br>11        |                   |              | 14<br>11        |                   | nV/√Hz<br>nV/√Hz  |

|                            | Input Noise Voltage                                                           | 0.1Hz to 10Hz                                                                          |   |                    | 3.5             |                   |              | 3.5             |                   | μV <sub>P-P</sub> |

| i <sub>n</sub>             | Input Noise Current Density                                                   |                                                                                        |   |                    | 1               |                   |              | 1               |                   | fA/√Hz            |

| V <sub>CM</sub>            | Input Common Mode Range                                                       | Guaranteed by CMRR                                                                     | • | V <sup>-</sup> +3V | ±68             | V+-3V             | V-+3V        | ±68             | V+-3V             | V<br>V            |

| C <sub>IN</sub>            | Common Mode Input<br>Capacitance                                              |                                                                                        |   |                    | 9               |                   |              | 9               |                   | pF                |

| C <sub>DIFF</sub>          | Differential Input Capacitance                                                |                                                                                        |   |                    | 5               |                   |              | 5               |                   | pF                |

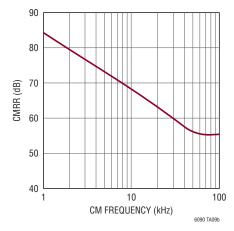

| CMRR                       | Common Mode Rejection Ratio                                                   | V <sub>CM</sub> = -67V to 67V                                                          | • | 130<br>126         | >140            |                   | 130<br>126   | >140            |                   | dB<br>dB          |

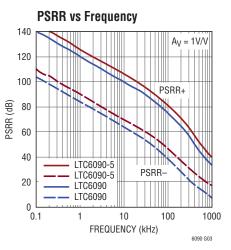

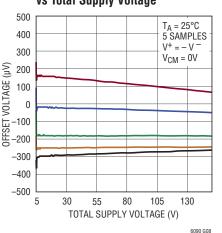

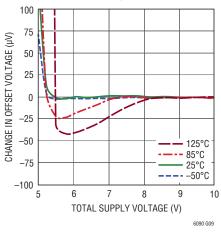

| PSRR                       | Power Supply Rejection Ratio                                                  | V <sub>S</sub> = ±4.75V to ±70V                                                        | • | 112<br>106         | >120            |                   | 112<br>106   | >120            |                   | dB<br>dB          |

| V <sub>OUT</sub>           | Output Voltage Swing High (V <sub>OH</sub> )<br>(Referred to V <sup>+</sup> ) | No Load<br>I <sub>SOURCE</sub> = 1mA<br>I <sub>SOURCE</sub> = 10mA                     | • |                    | 10<br>50<br>450 | 25<br>140<br>1000 |              | 10<br>50<br>450 | 25<br>140<br>1000 | mV<br>mV<br>mV    |

|                            | Output Voltage Swing Low (V <sub>OL</sub> ) (Referred to V <sup>-</sup> )     | No Load<br>I <sub>SINK</sub> = 1mA<br>I <sub>SINK</sub> = 10mA                         | • |                    | 10<br>40<br>250 | 25<br>80<br>600   |              | 10<br>40<br>250 | 25<br>80<br>600   | mV<br>mV<br>mV    |

| A <sub>VOL</sub>           | Large-Signal Voltage Gain                                                     | R <sub>L</sub> = 10k,<br>V <sub>OUT</sub> from –60V to 60V                             | • | 1000<br>1000       | >10000          |                   | 1000<br>1000 | >10000          |                   | V/mV<br>V/mV      |

6090f

#### **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications and all typical values are at  $T_J = 25^{\circ}C$ . Test conditions are V<sup>+</sup> = 70V, V<sup>-</sup> = -70V, V<sub>CM</sub> =  $V_{OUT} = 0V$ ,  $V_{\overline{OD}} = 0$  pen unless otherwise noted.

|                                    |                                                   |                                                                   |   | C-,       | I-SUFF   | IXES               | ŀ        |          |                    |              |

|------------------------------------|---------------------------------------------------|-------------------------------------------------------------------|---|-----------|----------|--------------------|----------|----------|--------------------|--------------|

| SYMBOL                             | PARAMETER                                         | CONDITIONS                                                        |   | MIN       | ТҮР      | MAX                | MIN      | ТҮР      | MAX                | UNITS        |

| I <sub>SC</sub>                    | Output Short-Circuit Current<br>(Source and Sink) | Supply Voltage = ±70V<br>Supply Voltage = ±15V                    | • | 50        | 90       |                    | 50       | 90       |                    | mA<br>mA     |

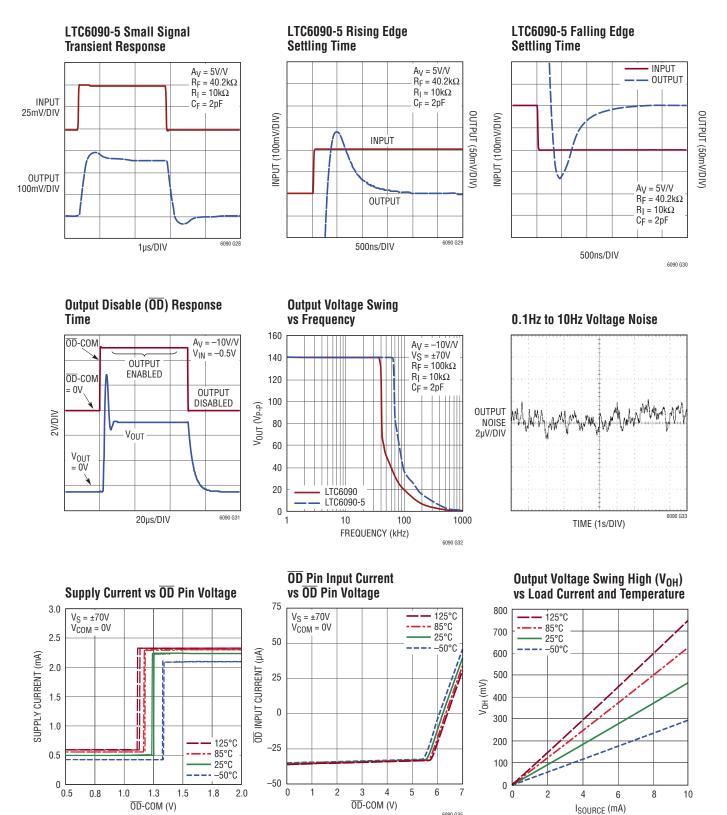

| SR                                 | Slew Rate                                         | $A_V = -4, R_L = 10k$<br>LTC6090<br>LTC6090-5                     | • | 10<br>18  | 21<br>37 |                    | 9<br>16  | 21<br>37 |                    | V/µs<br>V/µs |

| GBW                                | Gain-Bandwidth Product                            | $f_{TEST} = 20$ kHz, R <sub>L</sub> = 10k<br>LTC6090<br>LTC6090-5 | • | 5.5<br>11 | 12<br>24 |                    | 5<br>10  | 12<br>24 |                    | MHz<br>MHz   |

| $\Phi_{M}$                         | Phase Margin                                      | $R_{L} = 10k, C_{L} = 50pF$                                       |   |           | 60       |                    |          | 60       |                    | Deg          |

| FPBW                               | Full Power Bandwidth                              | $V_0 = 125V_{P-P}$<br>LTC6090<br>LTC6090-5                        | • | 20<br>34  | 40<br>68 |                    | 18<br>32 | 40<br>68 |                    | kHz<br>kHz   |

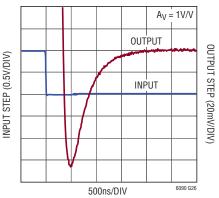

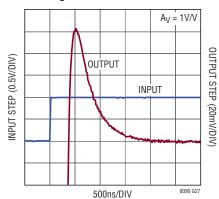

| t <sub>S</sub>                     | Settling Time 0.1%                                |                                                                   |   |           | 2<br>2.5 |                    |          | 2<br>2.5 |                    | μs<br>µs     |

| I <sub>S</sub>                     | Supply Current                                    | No Load                                                           | • |           | 2.8      | 3.9<br>4.3         |          | 2.8      | 3.9<br>4.3         | mA<br>mA     |

| V <sub>S</sub>                     | Supply Voltage Range                              | Guaranteed by the PSRR Test                                       | ٠ | 9.5       |          | 140                | 9.5      |          | 140                | V            |

| OD <sub>H</sub><br>OD <sub>L</sub> | OD Pin Voltage, Referenced to COM Pin             | V <sub>IH</sub><br>V <sub>IL</sub>                                | • | COM+1.8V  |          | COM+0.65V          | COM+1.8V |          | COM+0.65V          | V<br>V       |

|                                    | Amplifier DC Output<br>Impedance, Disabled        | $DC, \overline{OD} = COM$                                         |   |           | >10      |                    |          | >10      |                    | MΩ           |

| COM <sub>CM</sub>                  | COM Pin Voltage Range                             |                                                                   | • | V-        |          | V <sup>+</sup> - 5 | V-       |          | V <sup>+</sup> - 5 | V            |

| COMV                               | COM Pin Open Circuit Voltage                      |                                                                   |   | 17        | 21       | 25                 | 17       | 21       | 25                 | V            |

| COM <sub>R</sub>                   | COM Pin Resistance                                |                                                                   | • | 500       | 665      | 850                | 500      | 665      | 850                | kΩ           |

| TEMP <sub>F</sub>                  | Die Temperature Where TFLAG<br>Is Active          |                                                                   |   |           | 145      |                    |          | 145      |                    | °C           |

| TEMP <sub>HYS</sub>                | TFLAG Output Hysteresis                           |                                                                   |   |           | 5        |                    |          | 5        |                    | °C           |

| ITFLAG                             | TFLAG Pull-Down Current                           | TFLAG Output Voltage = 0V                                         | • | 70        | 200      | 330                | 70       | 200      | 330                | μA           |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC6090/LTC6090-5 is capable of producing peak output currents in excess of 50mA. Current density limitations within the IC require the continuous RMS current supplied by the output (sourcing or sinking) over the operating lifetime of the part be limited to under 50mA (Absolute Maximum). Proper heat sinking may be required to keep the junction temperature below the absolute maximum rating. Refer to Figure 7, the Power Dissipation section, and the Safe Operating Area section of the data sheet for more information.

Note 3: The LTC6090C/LTC6090I are guaranteed functional over the operating junction temperature range -40°C to 85°C. The LTC6090H is guaranteed functional over the operating junction temperature range -40°C to 125°C. Specifying the junction temperature range as an operating condition is applicable for devices with potentially significant quiescent power dissipation.

Note 4: The LTC6090C is guaranteed to meet specified performance from 0°C to 70°C. The LTC6090C is designed, characterized, and expected to meet specified performance from -40°C to 85°C but is not tested or QA sampled at these temperatures. The LTC6090I is guaranteed to meet specified performance from -40°C to 85°C. The LTC6090H is guaranteed to meet specified performance from -40°C to 125°C.

Note 5: This device includes over temperature protection that is intended to protect the device during momentary overload conditions. Operation above the specified maximum operating junction temperature is not recommended.

Note 6: Input bias and offset current is production tested with ±15V supplies. See Typical Performance Characteristics curves of actual typical performance over full supply range.

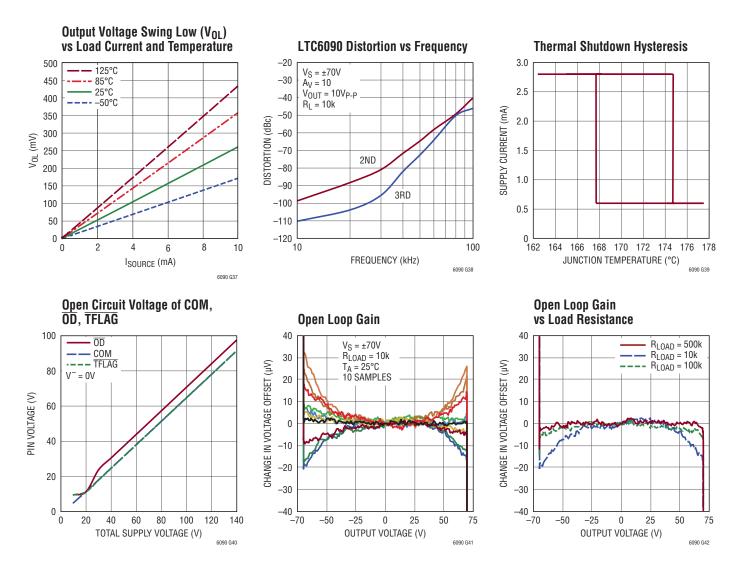

TCV<sub>OS</sub> Distribution

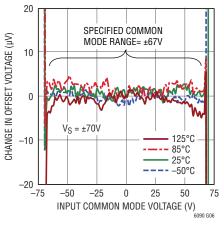

Change in Offset Voltage vs Input Common Mode Voltage

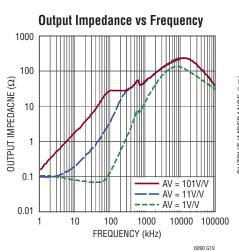

Output Impedance vs Frequency

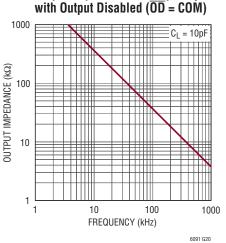

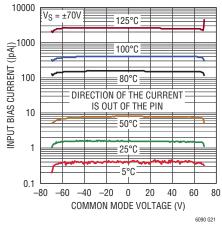

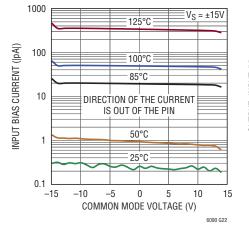

Input Bias Current vs Common Mode Voltage and Temperature

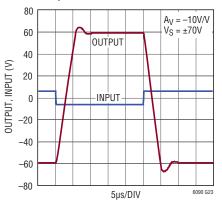

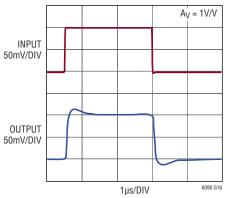

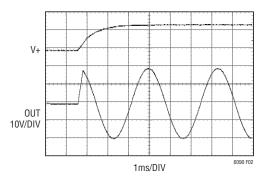

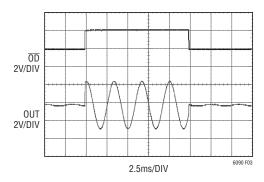

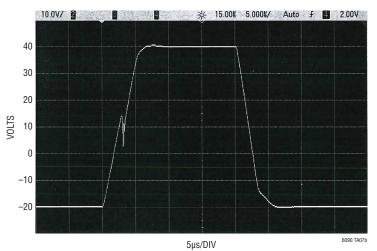

LTC6090 Large Signal Transient Response

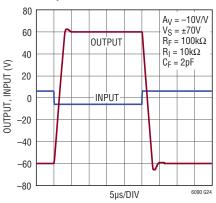

LTC6090-5 Large Signal Transient Response

#### LTC6090 Rising Edge Settling Time

6090 G36

6090fe

6090 G34

6090 G35

### PIN FUNCTIONS (S8E/FE)

**COM (Pin 1/Pin 1):** COM Pin is used to interface  $\overline{OD}$  and TFLAG pins to voltage control circuits. Tie this pin to the low voltage ground, or let it float.

-IN (Pin 2/Pin 4): Inverting Input Pin. Input common mode range is  $V^- + 3V$  to  $V^+ - 3V$ . Do not exceed absolute maximum voltage range.

+IN (Pin 3/Pin 5): Noninverting Input Pin. Input common mode range is  $V^-$  + 3V to  $V^+$  – 3V. Do not exceed absolute maximum voltage range.

**V**<sup>-</sup> (Pin 4, Exposed Pad Pin 9/Pin 8, Exposed Pad Pin 17): Negative Supply Pin. Connect to V<sup>-</sup> Only. To achieve low thermal resistance connect this pin to the V<sup>-</sup> power plane. The V<sup>-</sup> power plane connection removes heat from the device and should be electrically isolated from all other power planes.

**TFLAG** (Pins 5, 9/Pins 9, 17): Temperature Flag Pin. The TFLAG pin is an open drain output that sinks current when the die temperature exceeds 145°C.

**OUT (Pin 6/Pin 12):** Output Pin. If this rail-to-rail output goes below  $V^-$ , the ESD protection diode will forward bias. If OUT goes above V<sup>+</sup>, then output device diodes will forward bias. Avoid forward biasing the diodes on the OUT pin. Excessive current can cause damage.

V<sup>+</sup> (Pin 7/Pin 14): Positive Supply Pin.

**OD** (Pin 8/Pin 16): Output Disable Pin. Active low input disables the output stage. If left open, an internal pull-up resistor enables the amplifier. Input voltage levels are referred to the COM pin.

**GUARD (NA/Pins 2, 3, 6, 7, 10, 11, 13, 15):** Guard pins increase clearance and creepage between other pins. Pins 3 and 6 can be used to build guard rings around the inputs.

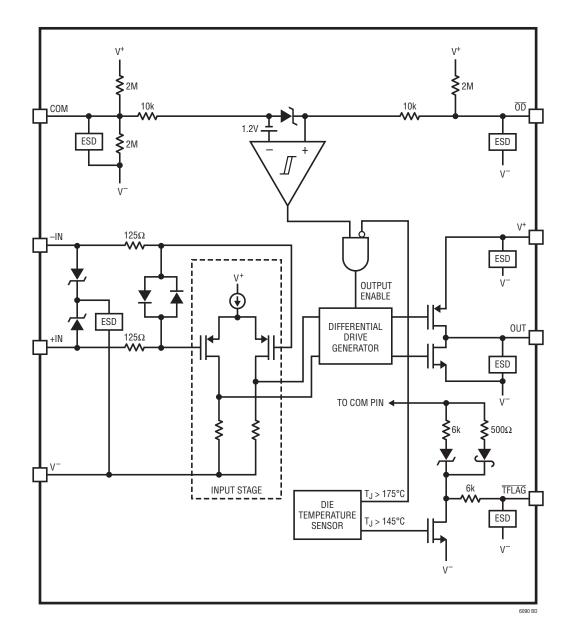

### **BLOCK DIAGRAM**

#### General

The LTC6090 high voltage operational amplifier is designed in a Linear Technology proprietary process enabling a railto-rail output stage with a 140V supply while maintaining precision, low offset, and low noise.

#### **Power Supply**

The LTC6090 works off single or split supplies. Split supplies can be balanced or unbalanced. For example, two  $\pm$ 70V supplies can be used, or a 100V and -40V supply can be used. For single supply applications place a high quality surface mount ceramic 0.1µF bypass capacitor between the supply pins close to the part. For dual supply applications use two high quality surface mount ceramic capacitors between V<sup>+</sup> to ground, and V<sup>-</sup> to ground located close to the part. When using split supplies, supply sequencing does not cause problems.

#### Input Protection

As shown in the block diagram, the LTC6090 has a comprehensive protection network to prevent damage to the input devices. The current limiting resistors and back to back diodes are to keep the inputs from being driven apart. The voltage-current relationship combines exponential and resistive until the voltage difference between the pins reach 12V.

At that point the Zeners turn on. Additional current into the pins will snap back the input differential voltage to 9V. In the event of an ESD strike between an input and V<sup>-</sup>, the voltage clamps and ESD device fire providing a current path to V<sup>-</sup> protecting the input devices.

The input pin protection is designed to protect against momentary ESD events. A repetitive large fast input swing (>5.5V and <20ns rise time) will cause repeated stress on the MOSFET input devices. When in such an application, anti-parallel diodes (1N4148) should be connected between the inputs to limit the swing.

#### Feedback Resistor Selection

To get the most accuracy, the feedback resistor should be chosen carefully. Consider an amplifier with  $A_V = -50$  and a 5k feedback resistor. A 1V input will cause the output to

rise to 50V, causing 10mA to flow through the feedback resistor. The power dissipated in the output stage will create thermal feedback to the input stage potentially causing shifts in offset voltage. A better choice is a 50k feedback resistor reducing the current in the feedback resistor to 1mA.

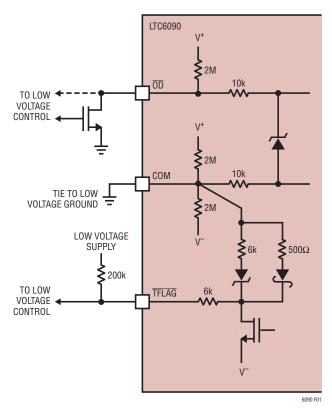

#### Interfacing to Low Voltage Circuits

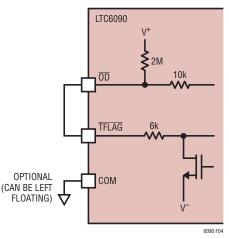

The COM pin is provided to set a common signal ground for communication to a microprocessor or other low voltage logic circuit. The COM pin should be tied to the low voltage ground as shown in Figure 1. If left floating, the internal resistive voltage divider will cause the COM pin to rise 30% above mid-supply. The COM, OD, and TFLAG pins are protected from overvoltage by internal Zener diodes and current limiting resistors. Extra care should be taken to observe the absolute maximum voltage limits between (OD and COM) and between (TFLAG and COM). Voltage limits between these pins must remain between -3V and 7V.

Figure 2. Starting Up

Figure 3. LTC6090 Output Disable Function

#### Output Disable

The  $\overline{OD}$  pin is an active low disable with an internal  $2M\Omega$  resistor that will pull up the  $\overline{OD}$  pin enabling the output stage if left open. The  $\overline{OD}$  pin voltage is limited by an internal Zener diode. When the  $\overline{OD}$  pin is brought low to within 0.65V of the COM pin, the output stage is disabled, leaving the bias and input circuits enabled. This results in 580µA (typical) standby current through the device. The  $\overline{OD}$  pin can be directly connected to the low voltage logic or an open drain NMOS device as shown in Figure 1.

For simplest shutdown operation, float the COM pin, and tie the  $\overline{\text{OD}}$  pin to the  $\overline{\text{TFLAG}}$  pin. This will float the low voltage control pins, and the overtemperature circuit will safely shutdown the output stage if the die temperature reaches 145°C.

Extra care should be taken to observe the absolute maximum voltage limits between ( $\overline{\text{OD}}$  and COM) and between ( $\overline{\text{TFLAG}}$  and COM). Voltage limits between these pins must remain between -3V and 7V.

When coming out of shutdown the LTC6090 bias circuits and input stage are already powered up leaving only the output stage to turn on and drive to the proper output voltage. Figures 2 and 3 show the part starting up and coming out of shutdown, respectively.

#### **Thermal Shutdown**

The TFLAG pin is an open drain output pin that sinks 200 $\mu$ A (typical) when the die temperature exceeds 145°C. The temperature sensor has 5°C of hysteresis requiring the part to cool to 140°C before disabling the TFLAG pin. Extra care should be taken to observe the absolute maximum voltage limits between ( $\overline{OD}$  and COM) and between ( $\overline{TFLAG}$  and COM). Voltage limits between these pins must remain between –3V and 7V.

Tying the the  $\overline{\text{TFLAG}}$  pin to the  $\overline{\text{OD}}$  pin will automatically shut down the output stage as shown in Figure 4. This will ensure the junction temperature does not exceed 150°C.

For safety, an independent second overtemperature threshold shuts down the output stage if the internal die temperature rises to 175°C. There is hysteresis in the thermal shutdown circuit requiring the die temperature to cool 7°C. Once the device has cooled sufficiently, the output stage will enable. **Degradation can occur or reliability may be affected when the junction temperature of the device exceeds 150°C.**

Figure 4. Automatic Thermal Output Disable Using the TFLAG Pin

#### Board Layout

The LTC6090 is a precision low offset high gain amplifier that requires good analog PCB layout techniques to maintain high performance. Start with a ground plane that is star connected. Pull back the ground plane from any high voltage vias. Critical signals such as the inputs should have short and narrow PCB traces to reduce stray capacitance which also improves stability. Use high quality surface mount ceramic capacitors to bypass the supply(s).

In addition to the typical layout issues encountered with a precision operational amplifier, there are the issues of high voltage and high power. Important consideration for high voltage traces are spacing, humidity and dust. High voltage electric fields between adjacent conductors attract dust. Moisture is absorbed by the dust and can contribute to board leakage and electrical breakdown.

It is important to clean the PCB after soldering down the part. Solder flux will accumulate dust and become a leakage hazard. It is recommended to clean the PCB with a solvent, or simply use soap and water to remove residue. Baking the PCB will remove left over moisture. Depending on the application, a special low leakage board material may be considered.

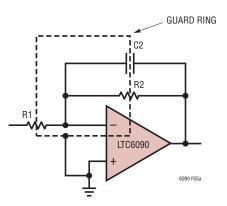

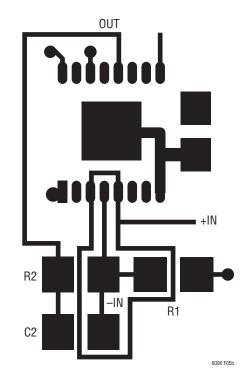

The TSSOP package has guard pins for applications that require a guard ring. An example schematic diagram and PCB layout is shown in Figures 5a and 5b, respectively, of a circuit using a guard ring to protect the –IN pin. The guard ring completely encloses the high impedance node –IN. To simplify the PCB layout avoid using vias on this node. In addition, the solder mask should be pulled back along the guard ring exposing the metal. To help the spacing between nodes, one of the extra pins on the TSSOP package is used to route the guard ring behind the –IN pin. The PCB should be thoroughly cleaned after soldering to ensure there is no solder paste between the exposed pad (Pin 17) and the guard ring.

Figure 5a. Circuit Diagram Showing Guard Ring

#### **Power Dissipation**

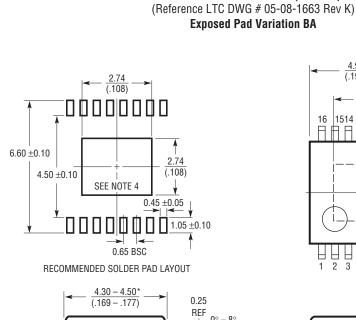

With a supply voltage of 140V it doesn't take much current to consume a lot of power. Consider that 10mA at 140V consumes 1.4W of power and needs to be dissipated in a small plastic SO package. To aid in power dissipation both LTC6090 packages have exposed pads for low thermal resistance. The amount of metal connected to the exposed pad will lower the  $\theta_{JA}$  of a package. An optimal amount of PCB metal connected to the SO package will lower the junction to ambient thermal resistance down to 33°C/W. If minimal metal is used, the  $\theta_{JA}$  could more than double (see Table 1). If the exposed pad has no metal beneath it,  $\theta_{JA}$  could be as high 120°C/W.

It's recommended that the exposed pad have as much PCB metal connected to it as reasonably available. The more PCB

metal connected to the exposed pad, the lower the thermal resistance. Use multiple vias from the exposed pad to the V<sup>-</sup> supply plane. The exposed pad is electrically connected to the V<sup>-</sup> pin. In addition, a heat sink may be necessary if operating near maximum junction temperature. See Table 1 for guidance on how thermal resistance changes as a function of metal area connected to the exposed pad.

The LTC6090 is specified to source and sink 10mA at 140V. If the total supply voltage is dropped across the device, 1.4W of power will need to be dissipated. If the quiescent power is included (140V  $\cdot$  2.8mA = 0.4W), the total power dissipated is 1.8W. The internal die temperature will rise 59° using an optimal layout in a SO package. A sub-optimal layout could more than double the amount of temperature increase due to power dissipation.

| EXAMPLE A                                                                                                                                    | EXAMPLE B                                                                                      | EXAMPLE C                                                                                                                                    | EXAMPLE D                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| TOP LAYER A                                                                                                                                  | TOP LAYER B                                                                                    | TOP LAYER C                                                                                                                                  | TOP LAYER D                                                   |

|                                                                                                                                              |                                                                                                |                                                                                                                                              |                                                               |

| <b>BOTTOM LAYER A</b>                                                                                                                        | BOTTOM LAYER B                                                                                 | BOTTOM LAYER C                                                                                                                               | <b>BOTTOM LAYER D</b>                                         |

|                                                                                                                                              |                                                                                                |                                                                                                                                              |                                                               |

| $\theta_{JA} = 43^{\circ}C/W$                                                                                                                | $\theta_{JA} = 50^{\circ}C/W$                                                                  | $\theta_{JA} = 57^{\circ}C/W$                                                                                                                | $\theta_{JA} = 72^{\circ}C/W$                                 |

| $\theta_{JC} = 5^{\circ}C/W$<br>$\theta_{CA} = 38^{\circ}C/W$                                                                                | $\theta_{JC} = 5^{\circ}C/W$<br>$\theta_{CA} = 45^{\circ}C/W$                                  | $\theta_{JC} = 5^{\circ}C/W$<br>$\theta_{CA} = 52^{\circ}C/W$                                                                                | $\theta_{JC} = 5^{\circ}C/W$<br>$\theta_{CA} = 67^{\circ}C/W$ |

| MINIMUM BOTTOM LAYER A                                                                                                                       | MINIMUM BOTTOM LAYER B                                                                         | MINIMUM BOTTOM LAYER C                                                                                                                       | 0 <sub>CA</sub> = 07 0/W                                      |

|                                                                                                                                              |                                                                                                |                                                                                                                                              |                                                               |

| \$                                                                                                                                           | *                                                                                              | 8                                                                                                                                            |                                                               |

| $\begin{array}{l} \theta_{JA} = 54^{\circ}\text{C/W} \\ \theta_{JC} = 5^{\circ}\text{C/W} \\ \theta_{CA} = 49^{\circ}\text{C/W} \end{array}$ | $\theta_{JA} = 57^{\circ}C/W$<br>$\theta_{JC} = 5^{\circ}C/W$<br>$\theta_{CA} = 52^{\circ}C/W$ | $\begin{array}{l} \theta_{JA} = 58^{\circ}\text{C/W} \\ \theta_{JC} = 5^{\circ}\text{C/W} \\ \theta_{CA} = 53^{\circ}\text{C/W} \end{array}$ |                                                               |

Table 1. Thermal Resistance as PCB Area of Exposed Pad Varies

In order to avoid damaging the device, the absolute maximum junction temperature should not be exceeded ( $T_{JMAX} = 150^{\circ}$ C). Junction temperature is determined using the expression:

$$\mathsf{T}_{\mathsf{J}} = \mathsf{P}\mathsf{D} \bullet \Theta_{\mathsf{J}\mathsf{A}} + \mathsf{T}_{\mathsf{A}}$$

where  $P_D$  is the power dissipated in the package,  $\theta_{JA}$  is the package thermal resistance from ambient to junction and  $T_A$  is the ambient temperature. For example, if the part has a 140V supply voltage with 2.8mA of quiescent current and the output is 20V above the negative rail sourcing 10mA, the total power dissipated in the device is (120V • 10mA) + (140V • 2.8mA) = 1.6W. Under these conditions the ambient temperature should not exceed:

$T_A = T_{JMAX} - (P_D \bullet \Theta_{JA}) = 150^{\circ}C - (1.6W \bullet 33^{\circ}C/W) = 97^{\circ}C.$

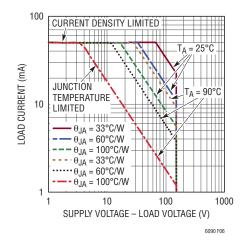

#### Safe Operating Area

The safe operating area, or SOA, illustrates the voltage, current, and temperature conditions where the device can be reliably operated. Shown below in Figure 6 is the SOA for the LTC6090. The SOA takes into account ambient temperature and the power dissipated by the device. This includes the product of the load current and difference between the supply and output voltage, and the quiescent current and supply voltage.

The LTC6090 is safe when operated within the boundaries shown in Figure 6. Thermal resistance junction to case,  $\theta_{JC}$ , is rated at a constant 5°C/W. Thermal resistance junction to ambient,  $\theta_{JA}$ , is dependent on board layout

Figure 6. Safe Operating Area

and any additional heat sinking. The six SOA curves in Figure 6 show the direct effect of  $\theta_{JA}$  on SOA.

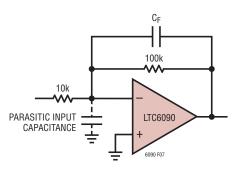

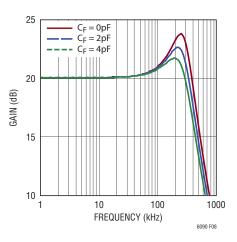

#### **Stability with Large Resistor Values**

A large feedback resistor along with the intrinsic input capacitance will create an additional pole that affects stability and causes peaking in the closed loop response. To mitigate the peaking a small feedback capacitor placed around the feedback resistor, as shown in Figure 7, will reduce the peaking and overshoot. Figure 8 shows the closed loop response with various feedback capacitors.

Additionally stray capacitance on the input pins should be kept to a minimum. With pA input current, the PCB traces should be routed as short and narrow as possible.

Figure 7. LTC6090 with Feedback Capacitance to Reduce Peaking

Figure 8. Closed Loop Response with Various Feedback Capacitors

#### Slew Enhancement

The LTC6090 includes a slew enhancement circuit which boosts the slew rate to  $21V/\mu$ s making the part capable of slewing rail-to-rail across the 140V output range in less than 7 $\mu$ s. To optimize the slew rate and minimize settling, stray capacitance should be kept to a minimum. A feedback capacitor reduces overshoot and nonlinearities associated with the slew enhancement circuit. The size of the feedback capacitor should be tailored to the specific board, supply voltage and load conditions.

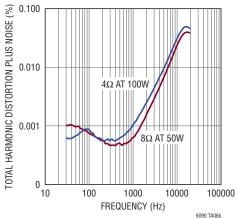

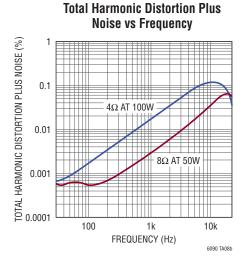

Slewing is a nonlinear behavior and will affect distortion. The relationship between slew rate and full power bandwidth is given in the relationship below.

$SR = V_0 \bullet \omega$

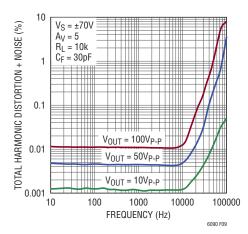

Where  $V_0$  is the peak output voltage and  $\omega$  is frequency in radians. The fidelity of a large sine wave output is limited by the slew rate. The graph in Figure 9 shows distortion versus frequency for several output levels.

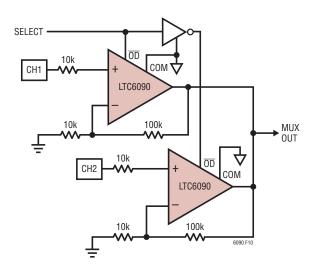

#### **Multiplexer Application**

Several LTC6090s may be arranged to act as a high voltage analog multiplexer as shown in Figure 10. When using this arrangement, it is possible for the output to affect the source on the disabled amplifier's noninverting input. The inverting and noninverting inputs are clamped through resistors and back to back diodes. There is a path for current to flow from the multiplexer output through the disabled amplifier's feedback resistor, and through the inputs to the noninverting input's source. For example, if the enabled amplifier has a -70V output, and the disabled amplifier has a 5V input, there is 75V across the two resistors and the input pins. To keep this current below 1mA the combined resistance of the R<sub>IN</sub> and feedback resistor needs to be about 75k.

The output impedance of the disabled amplifier is greater than  $10M\Omega$  at DC. The AC output impedance is shown in the Typical Performance Characteristics section.

Figure 9. Distortion vs Frequency for Large Output Swings

Figure 10. Multiplexer Application

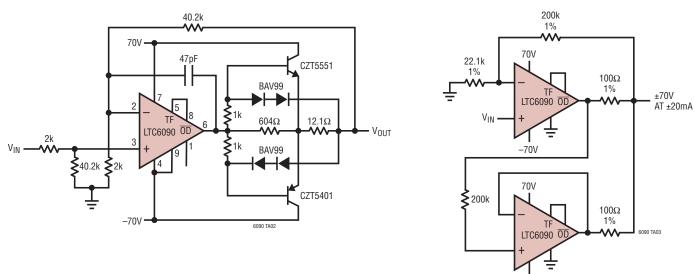

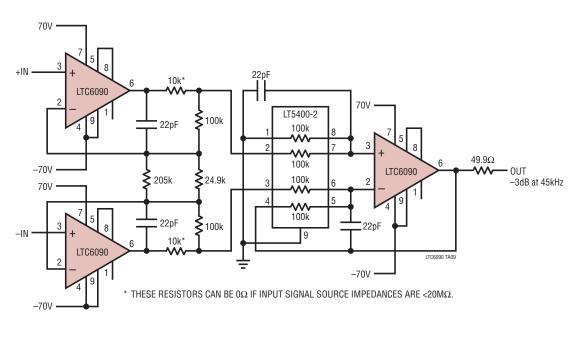

Gain of 20 Amplifier with a 40mA Protected Output Driver

Gain of 10 with Protected Output Current Doubler

-70V

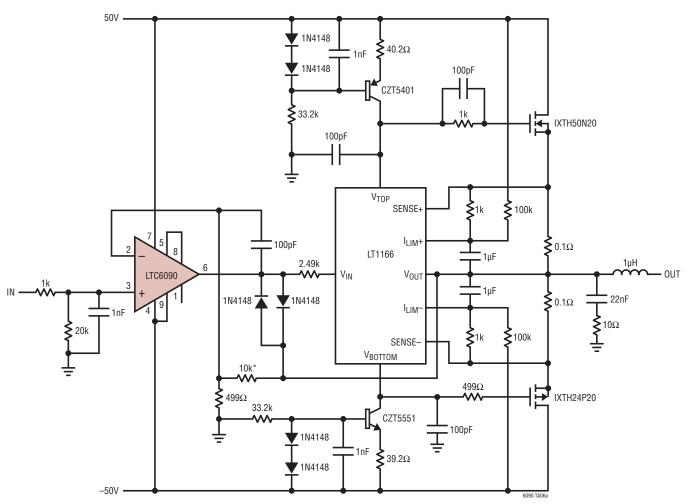

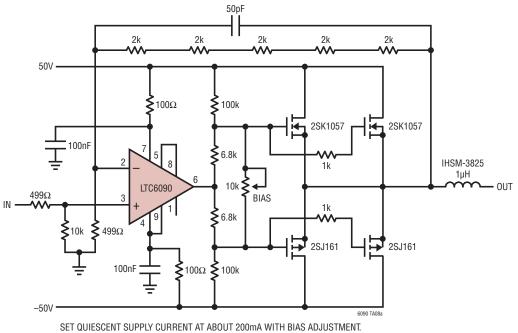

Audio Power Amplifier

$^{\ast}$  USE SEVERAL SERIES RESISTORS TO REDUCE DISTORTION (i.e. 5  $\times$  2k $\Omega).$

#### 75pF 10k 70V 4 2SK1057 IHSM-3825 1μΗ 499Ω - OUT LTC6090 Ŵ 3 IN 100Ω 2SJ161 **≤**10k ₹499Ω -70V 6090 TA07

#### High Current Pulse Amplifier

Simple 100W Audio Amplifier

SET QUIESCENT SUPPLY CURRENT AT ABOUT 200mA WITH BIAS ADJUSTMENT. SET QUIESCENT CURRENT TO 100mA IF PARALLEL MOSFETS ARE NOT USED (FOR  $8\Omega$  OR HIGHER).

LINEAR TECHNOLOGY

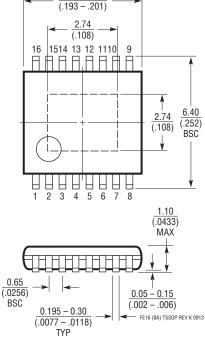

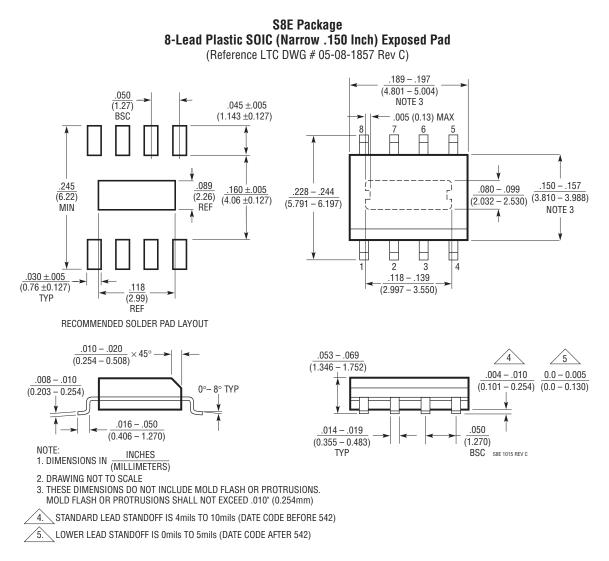

#### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/product/LTC6090#packaging for the most recent package drawings.

FE Package 16-Lead Plastic TSSOP (4.4mm)

4.90 - 5.10\*

NOTE:

- 1. CONTROLLING DIMENSION: MILLIMETERS

- 2. DIMENSIONS ARE IN MILLIMETERS (INCHES)

- 3. DRAWING NOT TO SCALE

4. RECOMMENDED MINIMUM PCB METAL SIZE FOR EXPOSED PAD ATTACHMENT \*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.150mm (.006") PER SIDE

### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/product/LTC6090#packaging for the most recent package drawings.

# **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                                | PAGE NUMBER |

|-----|-------|------------------------------------------------------------|-------------|

| Α   | 11/12 | Added ESD Statement.                                       | 2           |

| В   | 9/13  | Corrected schematics                                       | 16, 17, 18  |

| С   | 6/14  | Added LTC6090-5, Improved specs.                           | All         |

| D   | 5/15  | Removed ESD statement to reflect improved ESD performance. | 2           |

|     |       | Changed internal TFLAG circuit resistor values.            | 11, 12      |

|     |       | Updated Thermal Shutdown description.                      | 13          |

|     |       | Corrected application circuit resistor value.              | 19, 20, 21  |

| E   | 11/15 | Corrected resistor values                                  | 20, 21      |

#### Extended Dynamic Range $1M\Omega$ Transimpedance Photodiode Amplifier

### **RELATED PARTS**

| PART NUMBER                                                                               | DESCRIPTION                                                      | COMMENTS                                                                               |  |  |  |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| Amplifiers                                                                                |                                                                  |                                                                                        |  |  |  |

| LT1990                                                                                    | ±250V Input Range G = 1, 10, Micropower,<br>Difference Amplifier | Pin Selectable Gain of 1 or 10                                                         |  |  |  |

| LT1991                                                                                    | Precision, 100µA Gain Selectable Amplifier                       | Pin Configurable as a Difference Amplifier, Inverting and Noninverting Amplifier       |  |  |  |

| Matched Resistors                                                                         |                                                                  |                                                                                        |  |  |  |

| LT5400                                                                                    | Quad Matched Resistor Network                                    | Excellent Matching Specifications Over the Entire Temperature Range                    |  |  |  |

| Digital to Analog C                                                                       | onverters                                                        |                                                                                        |  |  |  |

| LTC2641/LTC2642                                                                           | 16-Bit V <sub>OUT</sub> DACs in 3mm × 3mm DFN                    | Guaranteed Monotonic Over Temperature                                                  |  |  |  |

| LTC2756 Serial 18-Bit SoftSpan I <sub>OUT</sub> DAC                                       |                                                                  | 18-Bit Settling Time: 2.1µs<br>Maximum 18-Bit INL Error: ±1 LSB Over Temperature       |  |  |  |

| Flyback Controllers                                                                       |                                                                  |                                                                                        |  |  |  |

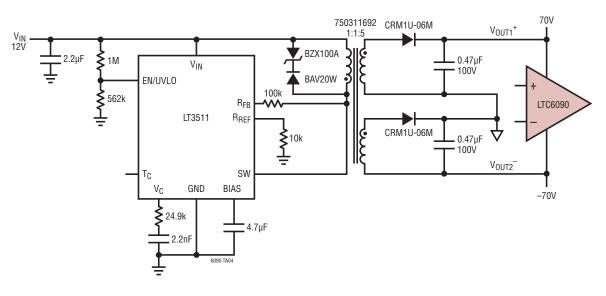

| LT3511 Monolithic High Voltage Isolated Flyback Converter                                 |                                                                  | r 4.5V to 100V Input Voltage Range, No Opto-Coupler Required                           |  |  |  |

| LT8300 100V <sub>IN</sub> Micropower Isolated Flyback Converter<br>with 150V/260mA Switch |                                                                  | $6V$ to 100V Input Voltage Range. $V_{\text{OUT}}$ Set with a Single External Resistor |  |  |  |

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

#### Analog Devices Inc.:

LTC6090HS8E-5#TRPBF LTC6090CS8E#TRPBF LTC6090IFE-5#PBF LTC6090HFE#PBF LTC6090IFE#PBF LTC6090HFE#TRPBF LTC6090IS8E-5#PBF LTC6090IFE-5#TRPBF LTC6090HS8E#PBF LTC6090CFE-5#PBF LTC6090IS8E#PBF LTC6090CFE#PBF LTC6090HFE-5#PBF LTC6090CFE-5#TRPBF LTC6090IS8E-5#TRPBF LTC6090HS8E-5#PBF LTC6090HFE-5#TRPBF LTC6090CS8E-5#TRPBF LTC6090CFE#TRPBF LTC6090CS8E#PBF LTC6090IFE#TRPBF LTC6090HS8E#TRPBF LTC6090IS8E#TRPBF LTC6090CS8E-5#PBF